- 非IC关键词

企业档案

- 相关证件:

- 会员类型:普通会员

- 地址:深圳市福田区振兴路109号华康大厦2栋216室

- 传真:0755-82564915

- E-mail:2909225061@qq.com

产品分类

相关产品

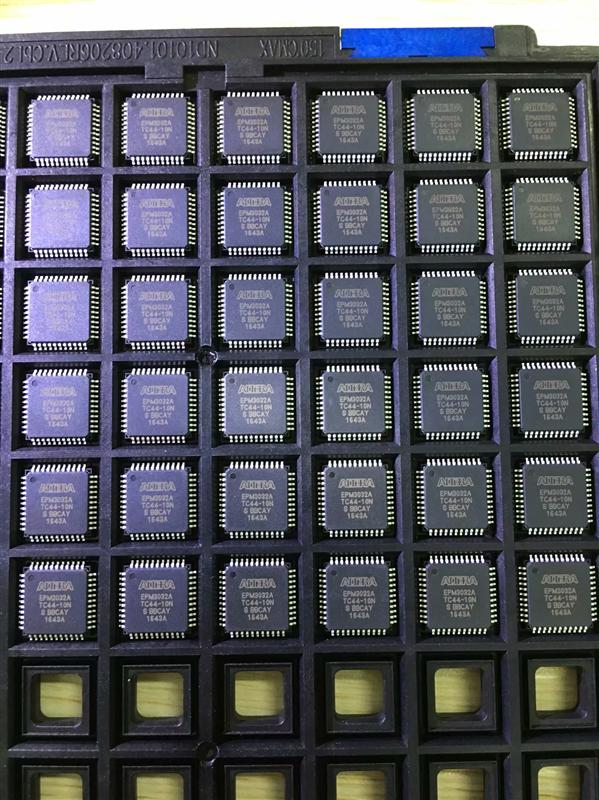

产品信息

■ High–performance, low–cost CMOS EEPROM–based programmable

logic devices (PLDs) built on a MAX® architecture (see Table 1)

■ 3.3-V in-system programmability (ISP) through the built–in

IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with

advanced pin-locking capability

– ISP circuitry compliant with IEEE Std. 1532

■ Built–in boundary-scan test (BST) circuitry compliant with

IEEE Std. 1149.1-1990

■ Enhanced ISP features:

– Enhanced ISP algorithm for faster programming

– ISP_Done bit to ensure complete programming

– Pull-up resistor on I/O pins during in–system programming

■ High–density PLDs ranging from 600 to 10,000 usable gates

■ 4.5–ns pin–to–pin logic delays with counter frequencies of up to

227.3 MHz

■ MultiVoltTM I/O interface enabling the device core to run at 3.3 V,

while I/O pins are compatible with 5.0–V, 3.3–V, and 2.5–V logic

levels

■ Pin counts ranging from 44 to 256 in a variety of thin quad flat pack

(TQFP), plastic quad flat pack (PQFP), plastic J–lead chip carrier

(PLCC), and FineLine BGATM packages

■ Hot–socketing support

■ Programmable interconnect array (PIA) continuous routing structure

for fast, predictable performance

■ Industrial temperature range

询价

询价